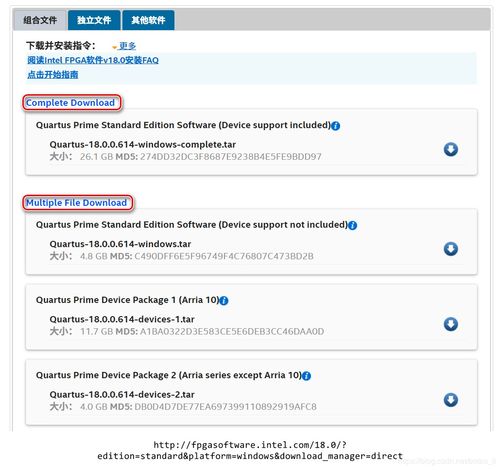

基于Quartus Prime Standard 18.0的FPGA基础开发流程详解

FPGA(现场可编程门阵列)开发是一个将硬件描述语言(HDL)转化为可在特定芯片上运行的数字电路的过程。Intel Quartus Prime Standard Edition 18.0是一款功能强大且广泛使用的FPGA开发软件。本文将详细介绍使用该软件进行基础FPGA开发的标准流程。

第一步:需求分析与设计规划

在打开软件之前,必须明确设计目标。例如,是创建一个简单的计数器、状态机还是接口控制器?确定输入输出信号、时钟频率、资源估算等。这一阶段通常用文本或框图完成,是后续所有工作的基础。

第二步:创建新项目

1. 启动Quartus Prime 18.0。

2. 点击“File” -> “New Project Wizard”。

3. 指定项目目录、项目名称和顶层设计实体名称(通常与项目名一致)。

4. 添加已有的设计文件(如.v或.vhd源文件)。如果新建项目,此步可跳过,后续再添加。

5. 选择目标FPGA器件家族、具体型号和封装。这是关键一步,需与开发板匹配。

6. 选择第三方综合、仿真工具(如有),然后完成向导。

第三步:设计输入 - 编写源代码

这是核心步骤,即使用硬件描述语言(如Verilog HDL或VHDL)描述电路功能。

- 点击“File” -> “New”,选择“Design Files”下的“Verilog HDL File”或“VHDL File”。

- 在打开的编辑器中编写代码。例如,一个简单的Verilog模块可能包括模块声明、输入输出端口定义、寄存器与线网声明以及功能描述(行为级或结构级)。

- 保存文件,并确保文件名与模块名一致(

.v为后缀)。

第四步:分析与综合

此步骤将HDL代码转换为门级电路网表,并检查语法和基本逻辑错误。

- 在“Processing”菜单下,点击“Start” -> “Start Analysis & Synthesis”。

- 软件会在“Tasks”窗口和“Messages”窗口显示进度和报告。任何错误或严重警告都需要在此阶段解决。

第五步:引脚分配与约束

告诉编译器设计中的逻辑端口对应到FPGA芯片的哪个物理引脚。

- 点击“Assignments” -> “Pin Planner”。

- 在弹出的界面中,根据开发板原理图,在“Location”列为每个输入输出信号指定具体的引脚编号。

- 还可以通过“Assignment Editor”设置时序约束(如时钟频率)。

第六步:完整编译

这是最耗时的步骤,包括综合、布局布线、时序分析和生成编程文件。

- 点击“Processing” -> “Start Compilation”,或工具栏的紫色三角形图标。

- 编译成功后,会生成一个

.sof(SRAM对象文件)用于后续下载,并会提供资源利用率、时序性能等详细报告。务必查看“Timing Analyzer”报告,确保设计满足时序要求(如无时序违例)。

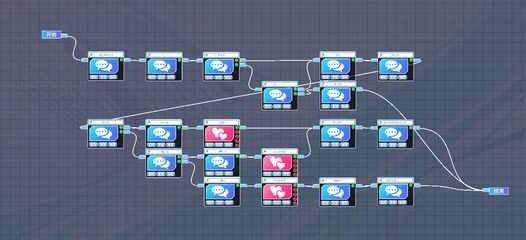

第七步:仿真验证(可选但强烈推荐)

在下载到板卡前,通过仿真验证逻辑功能是否正确。Quartus Prime自带仿真工具(University Program IP或与ModelSim协同)。

- 创建测试平台文件(Testbench)。

- 配置仿真工具,指定测试平台为顶层。

- 运行仿真,观察波形图,验证输出是否符合预期。

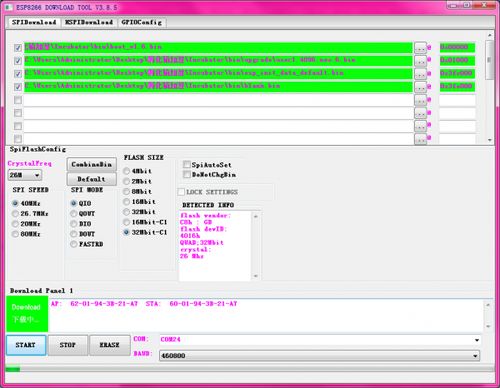

第八步:程序下载与配置

将编译生成的配置文件下载到FPGA开发板。

- 连接好JTAG或USB-Blaster下载线,给开发板上电。

- 点击“Tools” -> “Programmer”。

- 确保硬件被识别,然后添加生成的

.sof文件。 - 勾选“Program/Configure”,点击“Start”。进度条完成后,设计即被加载到FPGA中运行。

第九步:在线调试与验证

使用Quartus Prime的SignalTap II Logic Analyzer工具,可以实时捕获FPGA内部信号,就像在芯片内嵌入了一个逻辑分析仪,这对于调试复杂设计极其有用。

****

基于Quartus Prime Standard 18.0的FPGA基础开发流程是一个从抽象设计到物理实现的系统化工程。遵循“设计-综合-实现-验证”的迭代过程,并充分利用软件提供的分析和调试工具,是成功完成FPGA项目开发的关键。随着项目复杂度增加,还需要掌握更高级的约束设置、IP核集成和系统级设计方法。

如若转载,请注明出处:http://www.7gfun.com/product/66.html

更新时间:2026-02-28 02:51:39